Chip on Board (CoB) PCB Design Tips

Key Takeaways

-

Use thicker electroplated gold or ENIG to ensure strong die bonding.

-

Avoid via holes in epoxy areas or ensure they are completely plugged.

-

Maintain consistent solder wire lengths to reduce short-circuit risks.

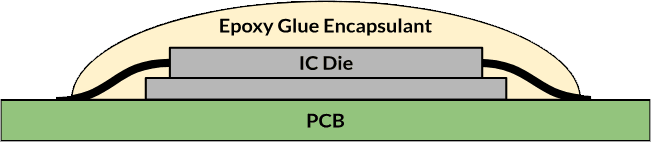

Simple Chip on Board (CoB) Diagram.

Chip on board (COB) is a method of circuit board manufacturing in which the integrated circuits are attached (wire-bonded directly) to a printed circuit board and covered by a blob of epoxy. COB eliminates the packaging of individual semiconductor devices and instead merges two levels of electronic packaging: level 1 (components) and level 2 (wiring boards). For this reason it may be referred to as packaging "level 1.5."

Chip-On-Board PCB Design Tips

|

Recommendation |

Description |

|

Surface Treatment |

|

|

Via Holes |

|

|

Positioning Points |

|

|

Silkscreen Logo |

|

|

Solder Wire Length |

|

|

Die Pad Size |

|

Chip-On-Board Design Types

COB packages offer several advantages over traditional packaging methods, including a smaller overall size, improved performance, and a lower cost of production. Three different methods are used to connect the terminal pads of the integrated circuit (or other semiconductor device) with the conductive traces of the printed circuit board in a COB PCB design.

Flip Chip on Board

FCOB, the solder is fluxed directly onto the PCB; it is not attached to the die. The chip will then be placed just like any other SMD component, and it will be reflowed along with other components. Therefore, some design for assembly (DFA) in terms of the footprint is needed to ensure reliable assembly, following similar guidelines for BGA pad sizing, but based on the bump size instead of ball size.

The solder mask and paste mask then need to be used to set the exposed pad size to be within the range that would normally be used in a BGA. If the bump pitch is large enough to leave large solder mask slivers, then use the solder mask to act as a dam (SMD pad).

Wire-Bonding

In wire bonding the chip is attached to the board with an adhesive. Each pad on the device is connected with a fine wire lead that is welded to the pad and to the circuit board. It’s best to encapsulate with an epoxy in order to protect the wire bonds and die from environmental exposure. This primarily prevents corrosion and protects the wires from mechanical damage. When creating the footprint for the wire bonding pads in the PCB, the pads are typically oversized. The parameters to be considered for the footprint include contact pad size, contact pad pitch, and contact pad shape.

Glob-Top

Glob-top is a variant of conformal coating used in chip-on-board assembly (COB). It consists of a drop of specially formulated epoxy or resin deposited over a semiconductor chip and its wire bonds to provide mechanical support.

Board Welding for Chip on Board

The welding process is categorized based on the shape of the solder joints: ball bonding and wedge bonding.

-

In chip-on-board (COB) applications, aluminum wire is often used, making wedge bonding the more common method.

-

Although ball bonding offers a stronger connection, it is also more costly compared to wedge bonding.

Choosing the Right Glue

After the chip is attached to the PCB, it is typically encapsulated with a thermally or UV-cured epoxy material or conformal coating to protect it and any wire bonded pads from damage. When selecting adhesives for a wafer (or die), the choice depends on the wafer's requirements for grounding or heat dissipation.

-

Silver glue, which necessitates high-temperature curing, is typically used if these properties are needed. This adhesive can be cured at 120°C for two hours or at 150°C for one hour.

-

Alternatively, anaerobic glue is used when electrical conductivity and heat conduction are not required. This type of adhesive cures naturally without needing high-temperature exposure by blocking contact with air. However, the reliability of anaerobic adhesives should be carefully assessed due to concerns about their longevity and potential to remelt.

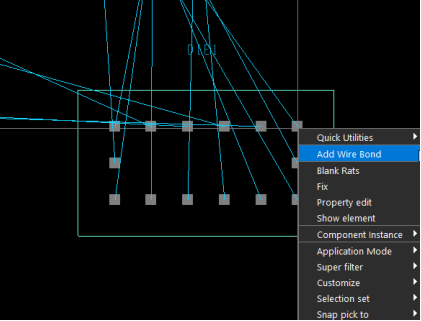

Adding wirebonds in Allegro X

How Allegro X Aids in CoB PCB Design

Allegro Chip-on-Board (CoB) capabilities provide a solution for designing and implementing advanced packaging technologies. The functionality includes a dedicated pad stack editor that allows designers to define specific pad stacks for bond fingers and die pads, ensuring optimal connection points for CoB devices.

Users can seamlessly establish design and mask layers while choosing bond pads during pin layout, which positions the bond layer on the top layer of the board, distinct from the device's bottom layer. The tools facilitate wire bonding through an intuitive wire bond edit mode, enabling precise alignment with die sides and customizable pad stack settings, including die numbering.

Furthermore, a 3D canvas view enhances visualization of the wire and bond connections, aiding designers in verifying the integrity of their connections. Cadence also offers extensive resources, including a searchable guide and practical examples, to support users in effectively implementing CoB technology in their designs.

To create a die symbol and connect wirebonds from the die to the PCB using the wirebond functionality in Allegro PCB Editor, follow these basic steps:

-

Create a wirebond die symbol in the Allegro Symbol Editor.

-

Place the wirebond die in the Allegro PCB Layout Editor by selecting Place > Manually.

-

Add the wirebonds.

-

Set the application mode in Allegro PCB Editor to “Wire Bond Edit.” Right-click on the Die Pin and choose “Add Wire Bond” to begin adding wire bonds. Click on the canvas with the left mouse button to position the bond fingers.

-

For more detailed instructions on how to build a die symbol and connect wirebonds from the die to the PCB using the wirebond functionality in Allegro PCB Editor, click here.

Leading electronics providers rely on Cadence products to optimize power, space, and energy needs for a wide variety of market applications. To learn more about our innovative solutions, talk to our team of experts or subscribe to our YouTube channel.