Low Power Circuit Design Strategies for PCBs

Key Takeaways

- Start with calculations to pinpoint significant power-draining components like MCUs and LEDs, ensuring targeted power-saving efforts.

- Choose components with low leakage and quiescent current.

- Implement power gating and clock gating to selectively reduce power in inactive circuit areas.

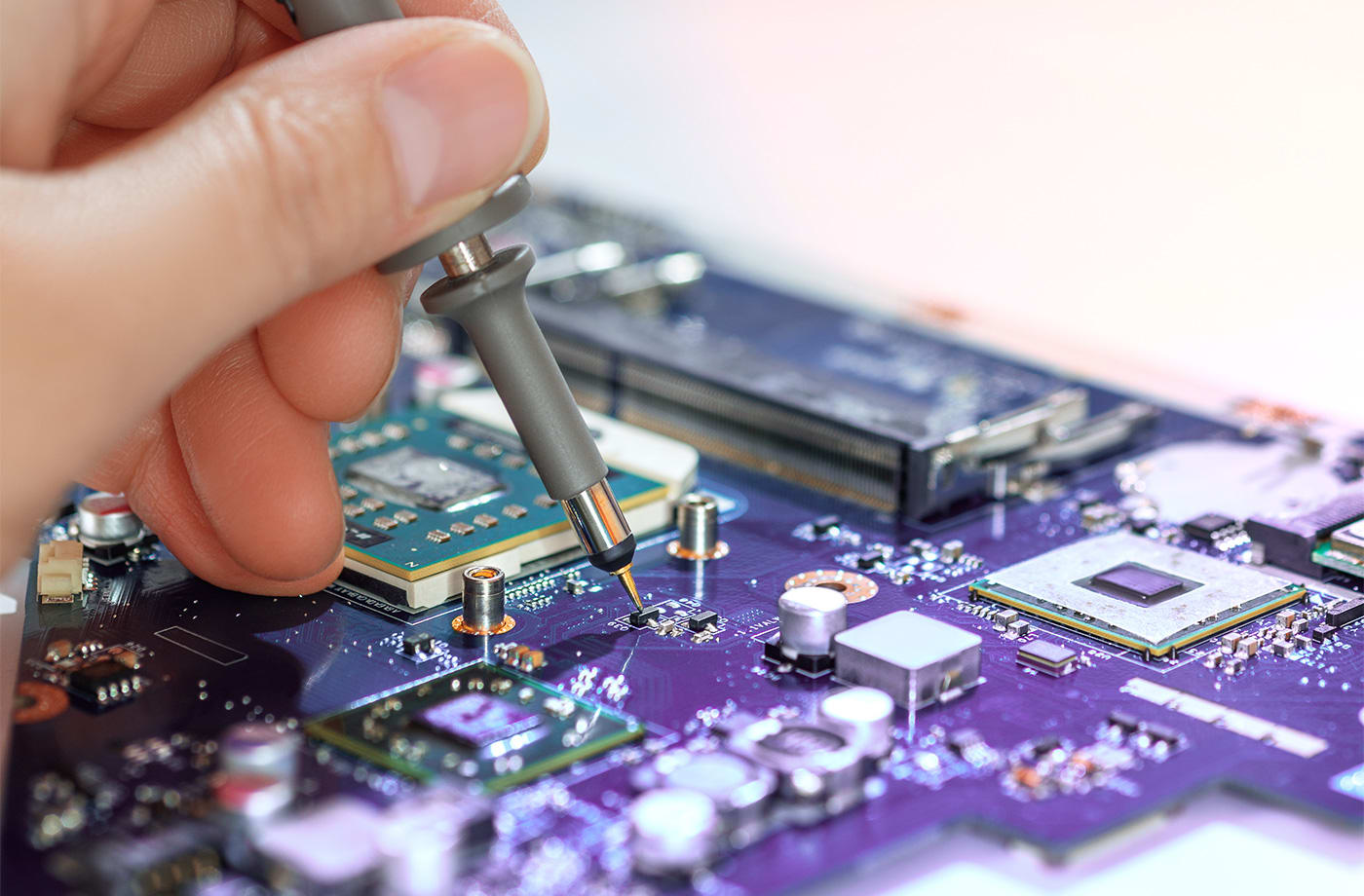

Low power circuit design involves a variety of techniques in minimizing power loss.

https://www.shutterstock.com/image-photo/electronics-repair-service-hand-female-tech-1926932294

Low power circuit design includes strategies focused on minimizing both dynamic and static power usage in your printed circuit boards. While selecting components with low power requirements is a crucial element, low power PCB design involves more comprehensive considerations to effectively manage power consumption.

Lower Power Circuit Designs Tips

|

Aspect |

Description |

|

Identify Major Power Consumers |

|

|

Component Selection |

|

|

PCB Size and Layers |

|

|

|

|

Reducing Switching Frequency and Duty Cycle |

|

|

EMI Management |

|

|

Minimizing Leakage |

|

Static and Dynamic Power

In the context of low-power circuit design, it's essential to distinguish between static and dynamic power.

- Dynamic power includes switching power, associated with the transistors turning on and off, and short-circuit power, which occurs during the transition period when both the pull-up and pull-down networks are momentarily conducting.

- Static power primarily results from leakage current, which is the current that flows through the transistor even when it is not actively switching.

Factors influencing both dynamic and static power components include activity, frequency, transition time, capacitive load, voltage, leakage current, and peak current.

Managing Components

When selecting active devices like MCUs, FPGAs, SoCs/SoMs, and other integrated circuits that handle data processing or manipulation, choose models that provide the necessary processing power while minimizing power consumption. Numerous MCUs designed for data-intensive tasks, as well as SoCs tailored for signal processing and similar functions, come equipped with a sleep mode feature. This feature allows the device to enter a low-power state, essentially powering down to conserve energy until a wake-up signal prompts it to resume activity.

Working with Memory

Designers often enhance power efficiency by incorporating a straightforward power switching control circuit that activates the flash memory using an available MCU GPIO pin only when required, drastically cutting standby power consumption. This method can raise reliability issues despite its benefits, particularly when several peripherals are connected via a common SPI bus. To address these concerns, the Ultra-Deep Power Down (UDPD) mode has been developed. This feature is built into the memory device itself and allows the MCU to manage power settings through the serial flash SPI, removing the need for external MOSFETs and conserving GPIO pins.

Stackup Design for Low Power

Designing your PCB stackup, regardless of the number of layers, involves accommodating stripline routing and strategically positioning power and ground planes on adjacent layers. This configuration enhances decoupling, significantly reducing the need for additional decoupling capacitors, ensuring power integrity on your board.

Advanced Low Power Circuit Design Solutions: Power Gating

Power gating involves selectively shutting off power to parts of a circuit when they are not in use. This is achieved by integrating power switches, such as transistors, into the circuit to control the power supply to individual components or sections of the board.

For instance, in a multi-functional device, power gating can be implemented by connecting a sensor or communication module's power supply through a microcontroller's MOSFET. When the device is dormant, and these functions are not needed, the microcontroller can turn off the MOSFET, cutting power to the components and significantly reducing idle power consumption.

Clock Gating

Clock gating involves controlling the clock signal supplied to various parts of a circuit. This method uses clock gates, multiplexers, or registers to disable the clock signal to components that are not actively computing or processing, preventing unnecessary clock cycles that consume power.

For instance, in a microprocessor, clock gating can deactivate the clock to an idle arithmetic unit while maintaining it for the active processor core. This selective clocking reduces dynamic power consumption by minimizing switching activity, which primarily contributes to power usage.

Complementing clock gating with dynamic voltage and frequency scaling (DVFS) enhances power management further. DVFS involves adjusting the voltage and frequency of the components based on their current workload and performance needs using voltage regulators, oscillators, or phase-locked loops (PLLs). This integrated approach ensures that the system not only conserves energy by reducing unnecessary clock signals, but also by adapting the power levels to match operational demands.

OrCAD X Features for Low Power Circuit Design

|

Feature |

Description |

|

Cross Section Editing |

Allows detailed setup of PCB stack-up, adjusting layers, thickness, and materials to meet design requirements. |

|

Via Arrays |

Provides versatile via placement options to enhance design flexibility and efficiency, helping to minimize power dissipation through optimized routing paths and reduced parasitic effects. |

|

Constraint Driven Routing |

Facilitates efficient routing with real-time constraint feedback, enhancing design manufacturability and functionality while ensuring optimal power usage through precise routing techniques and reduced signal interference. |

|

Signal Integrity Analysis |

Enables impedance and coupling analysis to optimize signal integrity and reduce power consumption, ensuring that high-speed signals are managed efficiently to avoid excessive power usage and minimize losses. |

|

Power Distribution Network (PDN) Design |

Supports the design of PDNs with low impedance, low noise, and high stability, incorporating decoupling capacitors, bypass capacitors, ferrite beads, and filters to stabilize voltage fluctuations and mitigate noise, leading to reduced power consumption. |

Embrace the potential of low power circuit design to create more efficient, cost-effective, and reliable PCBs. Visit our PCB Design and Analysis Software page and explore the capabilities of OrCAD X to elevate your low power circuit designs today.

Leading electronics providers rely on Cadence products to optimize power, space, and energy needs for a wide variety of market applications. To learn more about our innovative solutions, talk to our team of experts or subscribe to our YouTube channel.